My goal was to be able to measure and limit the output current to an accuracy of 1mA across the whole current range (0-5A) and the whole voltage range (0-30V). I wanted the current limiting circuit to be as quick as the voltage regulator but I found this isn't possible.

Basics of Current Sensing.

The idea is that we want to be able to set a maximum output current so that should something go wrong in the circuit powered by the supply, the circuit won't be damaged to much. The first part of the problem is actually measuring the current flowing.

While I will try and explain the basics here, I suggest looking at Linear Technologies Application note 105 as I think they do a better job.

The current sensing circuit measures the current flowing out of the power supply by inserting a small resistor in the power supply circuit and then measuring the voltage across this resistor. The resistor can be connected either between the positive side and the load (high-side) or between the load and the negative negative size (low-side).

High-side sensing is harder to implement as the inputs are likely close to the power supply rail (more on this later). The problem with low-side sensing is that if there is another path to ground that doesn't go via your sense resistor, you won't see any of it. I don't think this is a problem for my power supply as even if you tied the negative terminal to ground (and then grounded the negative side of the load) it would still complete the circuit via the ground part of the supply.

Current Sense Resistor

Choosing a current sense resistor and the amplifier to measure the voltage is quite tricky as you need to trade off the cost of heat dissipation in the sense resistor with the accuracy.

Working with the worst case settings of 5A, if I choose a 1 ohm resistor as the sense resistor then each mA of current generates 1mV across the resistor (which is easy to measure). However this will dissipate P = I^2 * R = 25W of power at full load. That's enough to require a heatsink and the increased temperature will cause the resistance value to vary (due to the resistors tempco). Also, this will drop 5V from the maximum voltage the power supply can deliver at full output.

On the other hand if I use a 1mOhm resistor then this will only burn 25mW and there is only 5mV drop. The problem then is that 1mA only generates 1uV on the resistor which is well below the offset voltage of many op amps.

The solution is to use 10-50mOhms which is still only 250mW - 1.25W, and 50mV - 250mV drop. Then 1mA will measure between 10uV and 50uV which is still pretty small but much better.

Current Sense Amplifiers

There are a few different ways of implement the current sensing circuit. Apart from high-side vs low-side you also have the choice of using a dedicated current sense module or to build one from op amps. Also, some of the high-side options are powered from the circuit they are monitoring and some can be run off an independent supply, There are modules that support digital output but this is no good unless they also provide an analog output as I need this for the current limiting circuit. Some have a fixed gain (or a set of fixed gains) where others can be configured with resistors.

A couple of the critical parameters for me were the ability to sense the current when the voltage is close to zero, having 1mA resolution (so therefore 5uV-25uV offset voltage) and an input range (common mode range) of 0 - 30V.

So I started by looking at dedicated, high-side current sense amplifiers and went through the manufacturers.

- From TI I found the INA-225, INA-250A2 to be the only ones that came close. Both had offeset voltages in the vecinity of 100uV or more which would mean I need at least a 200mOhm sense resistor which equates to 1V drop and 5W of power lost. The bandwidth is pretty bad too at between 5kHz and 250kHz.

- From Linear Technology I found the LT-1999 and LT-6105 that support he common mode voltage range I am after but both have silly offset voltages (300uV and 1.5mV).

- Maxim Integrated had two parts that fit my common mode voltage range - the MAX44284 and the MAX9643 although the MAX9643 had an offset voltage of 130uV. The MAX44284 looked perfect in that it supported separate supply voltage from the sense voltage, supports the full voltage range and has 10uV offset. The only downside is the thing is quite slow (between 3kHz and 400Hz and have settling time of 1.5ms).

All in all I was a bit disappointed with what was on offer. I'm not completely convinced that high-side monitoring is essentially and I was wondering if I could get away with using an op amp and monitoring the low side.

One of the issues with using an op amp to measure current on the high-side is that the quoted Common Mode Rejection Ratio (CMRR) apparently doesn't cover the case where the device is close to the rails. I don't have this issue as I am running most of the circuit at 40V so I can drive the MOSFET gate - so long as the op amp can handle this it won't be close to its rails.

So then I went looking for op amps

- Linear has the LT6015/6016/6017 which has 50uV offset and 3,2MHz Gain bandwidth product. This is close but I still need to use a 100mOhm sense resistor which means 2.5W power consumption.

- There is an LTC2057 which has over-the-top input (so rail-0.3 to rail+0.3), has 4uV offset and is quite low noise. Again it is slow (GBP of 1.5MHz) but not too bad.

- I looked at Max Integrated, searched for op amps with the required supply range, high CMRR and low offset voltage and one that caught my eye was MAX44241 which has an offset voltage of 5uV max! Also it has a bandwidth of 5MHz. Only down side is that it has a slightly lower voltage range (36V). The one issue with this part is that based on some quick googling it appears to be currently unavailable anywhere (certainly not for a while anyway)

- The TI OP27A looks perfect - fast, very low offset voltage, common mode range of -10 to 10V (which is fine for low-side sensing). Just one problem - they cost $55 each!

This looked pretty grim in that there are few choices and they are expensive or unavailable. Then it occurred to me that if I am sensing from the low side and say I configure the circuit to output 1V/1A then the maximum output will be 5V. I could use an op amp running at say 5V and this would work (well 5.5 would be better but anyway...).

Conveniently this post on the EEVBlog forum has a similar circuit and includes a parametric search of op amps. I looked through of those but the one that really stood out was the LTC2050HV that can run at 10V and has a 3uV offset and gain bandwidth product of 3MHz. Overall this looks pretty damn good and they cost about $3AUD in small quantities.

Conveniently this post on the EEVBlog forum has a similar circuit and includes a parametric search of op amps. I looked through of those but the one that really stood out was the LTC2050HV that can run at 10V and has a 3uV offset and gain bandwidth product of 3MHz. Overall this looks pretty damn good and they cost about $3AUD in small quantities.

Current Sense Circuit

The current sense circuit is quite simple in that it measures the voltage across the sense resistor and the amplifier feedback is setup to multiply the voltage to get 1A per volt.

The output matches pretty closely with what I want - it is pretty close to 1V/1A

However the response is a bit slow (as expected):

However the response is a bit slow (as expected):

Current Control Circuit

The usual current control circuit you see is like this where you do a diode-or between the output of a voltage error amplifier and the current error amplifier. Whichever of the two has a lower output will control the gate of the MOSFET. I found I had to buffer the monitor voltage as otherwise the capacitance used to compensate the current error amplifier messes with the current monitoring signal.

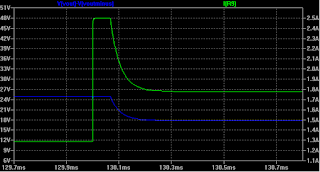

This did work and limits the current. As expected, the circuit takes some time between the output current rising and it clamping it to the limit. I don't think I can improve on this as I am limited by the speed of the current sense circuit. In the trace below I set the output voltage at 25V, I configured the load to switch between 1.3A and 2.5A and I set the current limit to 1,8A. You can see the load shoot up to 2.5A and then, about 100uS later, get clamped back to the limit. The current settles in around 200uS.

This is pretty much perfect I think. There is no way to make it react any faster and there will always be a short overshoot in current.

When the load falls away you can see the current undershoot slightly and then the output voltage and current climbs back up (slowly). I'm not bothered about the current undershoot but I noticed there is a significant voltage overshoot in the output which I don't like at all.

I thought about this for quite a while and figured out that the reason is that while the current error amplifier has control, the voltage error amplifier output shoots off to the positive rail. When the current error amplifier returns the voltage error amplifier has to come back down and this is dominated by the op amps slew rate.

I had an idea - what about if we use the current error amplifier to control the set voltage on the voltage error amplifier. If I do a diode-or between the set voltage and the current error output then when the current drops off it should not climb higher than the set voltage. Essentially something like this;

The one downside of this approach is that the output voltage will always be one diode drop higher than the set voltage. This means I can't take the supply down to below 0.6V unless I use a negative set voltage which isn't ideal. It does fix the problem very nicely however - here is the voltage/current trace when the current goes down.

The current/voltage recovers within about 8uS and there is no overshoot. Perfect!

I tried using another diode to get rid of the voltage offset but this doesn't work at low voltages. Maybe 0.6V might be a sensible minimum output voltage? I have to think about this.

What does the Jaycar supply do?

As before I thought it would be interesting to see how the Jaycar supply handles over current. As before the short answer is woefully!

In the scope trace below the yellow trace shows the current flowing (1V/1A). The dummy load was set for 2A and you can see the current peaks at around that. The supply was set for a current limit of 500mA and you can see the current rise to the full 2A and then the limit circuit kick in and bring it back down. The green trace shows the output voltage while this is happening and it goes from near zero to just under 6V

It is just so slow though. It takes 3-4ms for the current to be limited. Checkout the slow rise time on the voltage too. Crazy!

Next I hope to get some parts and test the current limiter on the breadboard.